目前,覆铜板(CCL)介电常数取值方面主要考虑介质层对其影响,鲜少讨论铜箔的不同是否会影响材料的介电常数、损耗等介电性能。随着在5G通信基站以及更高的以太网、云服务器的发展,PCB朝着高频高速方向发展,对电阻、阻抗、损耗的控制精度要求越来越高。因此在PCB设计和生产中,了解铜箔对材料的介电性能影响,在实现精准的电阻和阻抗控制以及降低损耗方面具有重要意义。

一、铜箔粗糙度对直流电阻的影响

在PCB设计中,一些电子产品对线路板内传输线的直流电阻有一定要求。目前,行业对有直流电阻要求的线路板一般控制在设计值的±10%范围,部分要求控制在±5%。根据欧姆定律:

其中,R为电阻(Ω);ρ为铜电阻率(0.017593Ω·mm2/m)。

电阻仅与线路长度和横截面积有关。但一些研究表明:在相同的线宽及线路长度下、使用不同粗糙度的铜箔,其传输线的直流电阻不同。如图1所示是18μm的VLP、RTF、STD三种铜箔的板材,各设计十组长度为254mm,线宽分别为0.15mm、0.2mm、0.25mm的传输线,经过内层蚀刻后使用微电阻仪(Ohm Meter)测量各线宽下的电阻。从图1中可以看出,表面粗糙度最大的 STD铜箔直流电阻最大,其次是RTF、VLP铜箔,相同设计下RTF铜箔较VLP铜箔的直流电阻偏大4%~6%。

图1 PI薄膜传输线长254mm直流电阻随铜箔类型变化趋势

此外,根据现有铜箔规格厚度按照称重法计量,不同铜箔类型的加工过程中经微蚀刻后,铜面厚度以及覆盖有机涂层厚度存在差异,这导致相同规格厚度的有效导体厚度不同,也会造成相同线宽下有效导体截面差异。

二、铜箔粗糙度对直流电阻的影响

介电常数是PCB阻抗设计中不可或缺的因子,是描述某种材料放入电容器中增加电容器存储电荷能力的物理量,属于材料本身所固有的电气特性。在IPC-650测量介电常数的标准中,含铜与无铜的板材都可以作为测试样品。此前,根据材料的介电常数依赖于板材中树脂与玻纤的成分以及所占比值,不受铜箔的影响。然而,铜箔本身也具有一定介电性能和储能能力,影响覆铜板整体的介电常数;在铜箔与板材压合过程中,铜箔毛面嵌入在树脂内,类似于铜箔填充到树脂中,改变树脂的介电常数值。

一些研究通过反推统计法验证了铜箔表面粗糙度与板材介电常数的关系。如图2是采用18μm的VLP、RTF、STD三种铜箔与2张1080(RC69%)压合制作芯板,并使用完全相同的叠层并设计完全相同的多组阻抗条(coupon)。通过测量各附连扳(coupon)的内层阻抗值,利用测量对应线宽、介厚、铜厚等数据进行反推统计Dk均值,对100组数据进行统计所得的结果。

从图中可以看出,1080配置VLP、RTF、STD的介电常数分别为3.073、3.148、3.245,粗糙度越低的铜箔对应的Dk值越小。

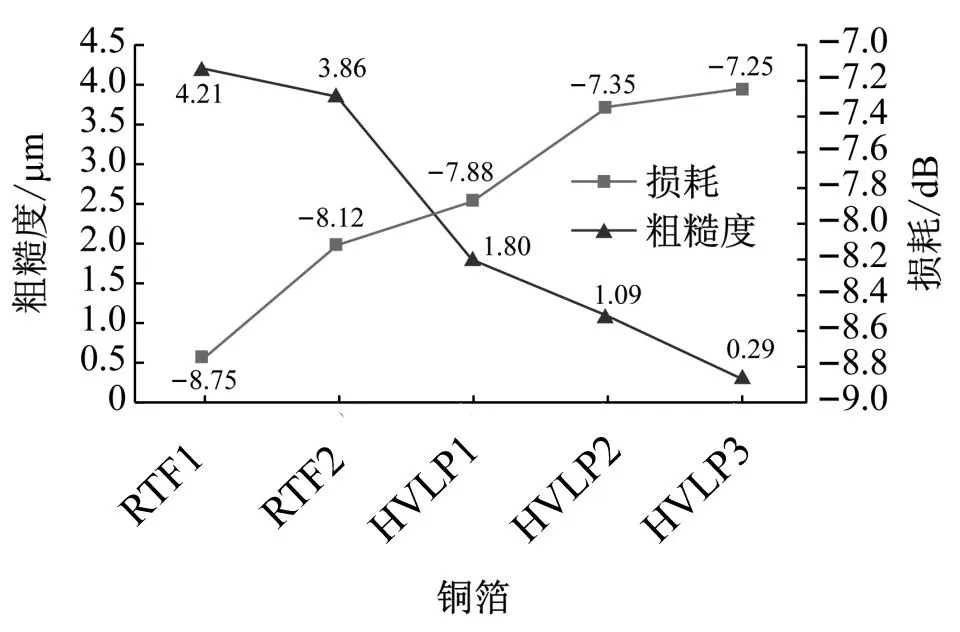

三、不同粗糙度铜箔对信号损耗的影响

在高频高速信号传输中,传输线受到变频场的作用产生趋肤效应(skin effect),即电流趋向导体表面富集。如果导体表面粗糙度大于趋肤深度时,信号传输仅在粗糙度的厚度范围内进行,使传输信号的驻波、反射越来越严重,并导致信号传输路径变长,增加传输损耗。

在PCB传输线设计中,可根据 Hammerstad传输线模型模拟导体表面粗糙度对损耗影响,是将光滑导体的信号损耗乘以Hammerstad系数,公式如下所示:

其中,Ksr 为趋肤系数,hRMS为表面粗糙高度的均方根(Rq),δ为趋肤深度。趋肤深度受传输频率的影响,有:

根据经典损耗理论,传输线总损耗根据公式:

考虑到趋肤效应,传输线的总损耗通过修正有:

其中,αt为总损耗,αc为无趋肤效应的导损,αd为介损。以带状线为例,带状线的导体损耗和介质损耗有以下公式:

其中,f为信号传输频率,εr 为介电常数,t为传输线铜厚,w为传输线宽度,b为两地之间的介质厚度,常数,tan δ 为介质损耗因子。从上损耗理论损耗的影响因素来看,铜箔表面粗糙度影响传输线的导体损耗,粗糙度越大,趋肤效应中的Hammerstad系数越大,导损、总损耗越大。因此,低粗糙度铜箔有利于降低高频高速信号的损耗。

四、总结

综上所述,铜箔的粗糙度对高频PCB的电性能有着重要影响。随着5G的高速发展,应用于高频电路上的铜箔也必然要求表面粗糙度越来越低。花园新能源正在保证剥离强度的基础上致力于低粗糙度铜箔的研发,加速高频用铜箔国产化。

英文

英文 中文

中文